System-Level Engineering &

Diagnostics.

Bridging the "no-man's land" between 10W-2kW switch mode power conversion and Assembly-level firmware. Specialising in deterministic control and architectural integrity.

LDX #$02 ; LOAD RECENT_DEPLOYMENTS

Project Case Studies

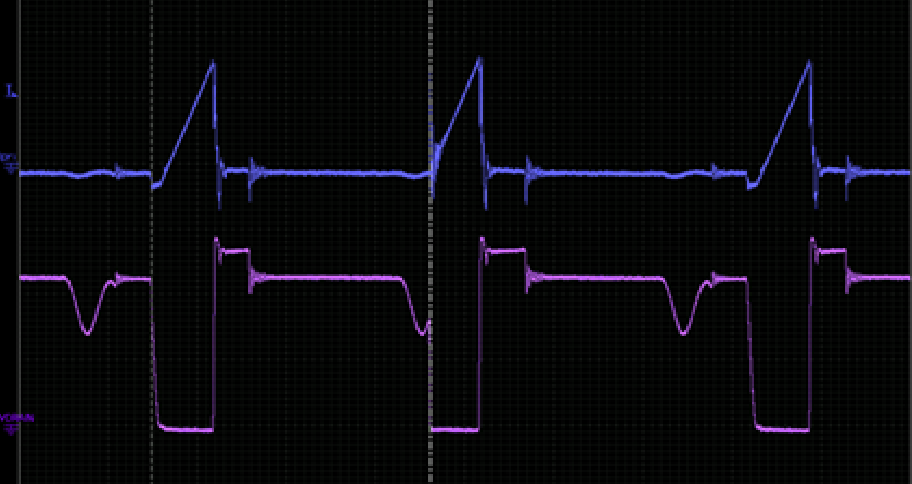

50W Flyback Converter Optimization

Investigated and resolved critical ringing and excessive thermal stress in a quasi-resonant / zero voltage switching flyback prototype. Implemented a deterministic state-machine in C to optimize valley switching and implemented active clamp control. Performed rigorous margin analysis and retuned the control logic, achieving stable regulation across all operating conditions.

if (fault_flag) {

DISABLE_ALL_PWM();

return;

}

uint16_t next_duty = calculate_duty();

UPDATE_TIM1_CCR(next_duty);

}

High-Speed GaN Inverter Digital Control

Architected and coded the bare-metal C control loop for a high-frequency GaN inverter. The project required highly deterministic execution to ensure nanosecond-precision dead-time generation and fault-handling. Optimized the microcontroller's hardware timers and interrupt priorities, validating the C-code logic entirely in simulation before successful deployment on the physical target.

LDA #$01 ; LOAD SERVICE_HIERARCHY

The "Fixer" Ladder

The Rescue Mission

3–5 day deep-dive forensic diagnostics for critical failures: overheating, MOSFET destruction, or control loop instability in active prototypes.

- + Transient Analysis

- + Stability Margin Audit

- + Thermal Stress Testing

System Architecture

Hardware-software partitioning. Deterministic analysis of what lives in silicon, FPGA logic, or microcontroller code.

- + Bare-Metal C & Asm

- + Verilog FPGA Design

- + Deterministic Control

Advanced Simulation & Synthesis

High-fidelity piece-wise linear simulation for complex power stages. We validate production logic before hardware arrival through the implementation of digital logic using the SIMPLIS C-code DLL.

- + Piece-Wise Linear Sim

- + Digital Synthesis

- + C-Code DLLs

The Forensic Diagnostic Lab.

Validation and stress-testing that internal teams cannot perform. A state-of-the-art facility dedicated purely to validation, stress-testing, and breaking what shouldn't break.

> INIT SYSTEM_SCAN...

> DETECTING_TRANSIENT [V_DS_MAX: 650V]

> LOOP_STABILITY_MARGIN: WARNING (32deg)

> APPLYING_COMPENSATION_NETWORK...

> RECALCULATING...

> LOOP_STABILITY_MARGIN: OPTIMAL (65deg)

JSR $C000 ; JUMP TO HYBRID_ENTITY

Bridging the Gap.

Most bugs hide in the "no-man's land" between 10W-2kW switch mode power conversion and embedded firmware. We possess the rare dual-competency to debug high-speed transients on an oscilloscope while simultaneously optimizing Assembly-level control loops.

We don't just fix the hardware; we write the logic that drives it.

Project Intake

Submit your failure mode. If it's a fit, we move from "stuck" to "decided" in under 10 days.